# Extending Microelectronics Education: Online Process/Device Simulation Laboratory

# <sup>1</sup>Chinmay K Maiti and <sup>2</sup>Ananda Maiti

<sup>1</sup>Department of Electronics and ECE, IIT Kharagpur 721302 India ckm@ece.iitkgp.ernet.in<sup>1</sup>; <sup>2</sup>School of Computer Science, VIT University, Vellore 632014 TN India ananadamaiti@live.com<sup>2</sup>

## Abstract

The aim of this work is to develop and implement an interactive online internet-based teaching laboratory for microelectronic education. The possibility of teaching semiconductor process and device simulation in a highly cost-effective manner by taking the advantages of high speed internet and available process/device simulation tools is explored.

## 1. Introduction

For microelectronics engineering courses, IC fabrication laboratory is essential for hands-on experience. But equipping an IC fabrication laboratory is a major expense for any institution and its maintenance is also difficult. Teaching assistants are required to set up and maintaining the laboratory, instruct in the laboratory, and grade laboratory reports. These time-consuming and costly tasks result in relatively low laboratory infrastructure usage, especially considering that laboratories are utilized only when equipment and teaching assistants are both available. As a result, in most undergraduate and virtually in all master programs in microelectronics there are courses on device physics and processing technology (frequently as one single course). Currently, the courses are taught from standard text books on MOS and bipolar including device fabrication. Although there is a very strong connection of device modeling and processing technology, very limited resources are available which bridges the gap [1]. With the recent advances in technology CAD (TCAD), various aspects of technology cross-sections involving bipolar, CMOS, SOI MOSFETs, group-IV and III-V HBT technologies can be illustrated by using TCAD in process/device analysis and design. The advantage is the fact that these simulations are immediately available to the teacher and the student can simulate and explore process and device design.

Process and device simulation is commonly used for the design of new VLSI technologies. Simulation programs also serve as exploratory tools in order to gain better understanding of process and device physics. Technology computer aided design is essential to the design of modern integrated circuit fabrication processes. TCAD tools not only provide modeling of real processes, but allow predictive simulation during technology research and development. It also works as an integrated system to allow efficient exploration of technology options. Sensitivity and statistical analyses using an integrated TCAD system provide rapid technology characterization, including the examination of process extremes, before fabrication. This predictive capability of TCAD reduces technology design time, and enables optimized manufacturable designs. Tools supporting the TCAD cover a wide range of disciplines that includes process and device simulation, compact models, parameter extraction, interconnect simulation, and circuit simulation. Virtual Wafer Fabrication (VWF) is a computing environment that solves the problems outlined above. The recent development of fully integrated TCAD or Virtual Wafer Fabrication (VWF) tools is largely due to the frustration experienced by device and process engineers attempting to use independent simulation tools e.g., a process simulator and a device simulator as each program has its own form of input/output format.

Teaching of IC Fabrication theory courses is very frustrating when using conventional techniques to describe complex concepts such as diffusion and ion implantation techniques,

cross-sectional diagrams of ICs, changes in concentration of doping level in transistors, different levels of fabrication steps and keeping a track of the sequence of IC fabrication steps. An integrated e-learning environment for web-based online lecture-tutorial-laboratory (L-T-L) module with laboratory components for final year undergraduate and postgraduate students is necessary for microelectronics courses. The module should include the functionality to present live lectures and demonstrations to diversely located students. In addition, students should be able to run simulation experiments either individually or collaboratively with the majority of the functionality currently offered by the conventional laboratories. The purpose of the proposed process/device simulation laboratory is to provide the student a glimpse of the various aspects of semiconductor technology, development of new process technologies and the prediction of the behavior of new device structures. The use of TCAD in semiconductor manufacturing is twofold: First, it models the complex flow of semiconductor fabrication steps and ends up with detailed information on geometric shape and doping profile distribution of a semiconductor device. Second, the device simulation uses the information of the first step to calculate the characteristics of semiconductor devices. The resulting device characteristics are used for fitting circuit simulation models. A technology computer aided design (TCAD) process/device simulation laboratory has been developed and is in use for imparting hands-on simulation laboratory experience to the students (available at http://lod.iitkgp.ernet.in/netlab/).

The objectives of the work presented in this paper is to describe the development, implementation and dissemination of an interactive online process and device simulation laboratory for Integrated Circuit (IC) Fabrication courses offered by many universities. The effectiveness and evaluation data collected from the students to measure student learning and to assess the strengths and weaknesses of the laboratory module will also be discussed.

## 2. Process and Device Simulation

Efforts to scale down the device size and increase the performance of integrated circuits are becoming more challenging than in the past. Availability of increasingly powerful computers and TCAD softwares has now made possible accurate multidimensional simulation of realistic device structures and physics. In fact, TCAD played an important role in guiding electronics development in the 1990s. TCAD does more than simply improving on the scaling laws: it has actually replaced some of the expensive and slow fabricate-test-redesign development process. Simulation allows one to design devices several generations ahead without developing or purchasing expensive new fabrication equipment. In fact, the ultimate platform for TCAD would be a "Virtual Fabrication." That is, all aspects of the electronics system production will be simulated before the fabrication.

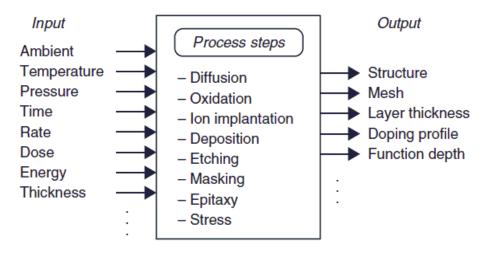

Figure1. Process steps involved in the manufacturing of an IC. Several hundred steps are involved.

#### 2.1 Process Simulation using SUPREM

Process simulation involves the numerical solution of equations describing the physics of diffusion, oxidation, lithography, ion implantation, and etching and deposition steps, resulting in geometry and doping profiles that define a device. Process simulation methodology requires the detailed semiconductor fabrication process flow including numerous fabrication details, like angle of incidence of ions implanted in ion implantation process steps or etch rate distribution as a function of the local angle of the etched layer surface. The simulation starts with the blank wafer and ends with device/circuits. Process simulation predicts the structural and doping profiles of the devices on the basis of the key processing parameters, for example, implant dose, energy and anneal time and temperature. With the maturity of TCAD tools, real wafer fabrication can now be emulated by process simulation, from which realistic device structures and doping profiles can be generated, and transistor performance can be predicted through device simulation with a reasonable accuracy.

The manufacturing of an IC requires many complex processing steps, many of which are illustrated in Figure 1, with each of these steps containing numerous possible variations in process controls, and may take several weeks to complete. During the design stages of a device/circuit, a large number of experiments have to undertaken to determine appropriate settings of certain process parameters, as well as of the layout topology and the geometrical dimensions best suited to meet the device specifications. After a process has been well characterized, simulation can be used to investigate the effect of parameter variation with the necessity of experimental design. Process simulation models semiconductor manufacturing steps such as oxidation, implantation, diffusion, etching, deposition and lithography. Process simulation has evolved with increasing levels of sophistication from the earliest models for process steps. The computer implementation of such models led to the evolution of SUPREM simulator SUPREM I in 1977, followed by enhanced versions up to the two-dimensional version SUPREM IV [2]. In the proposed simulation laboratory we use SUPREM II and a sample run sheet is shown in Figure 2.

| e Edit View Favorites Tools Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                  |                              | • 🖻 🕂 🛪 🛃 Google | 🗴 🌒 Convert 🔻 🔂 Select        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|-------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                              |                  |                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | irch • + 🗇 • 💠 • 🥥 📓 • 🏠 Bookman                                                                                 | ks • 🦃 Check • 👪 Translats • | 🐂 AutoFill 🔹 🍠   | 🔩 + 🍥 Sign In                 |

| Favorites 🛛 🙀 Google 🖓 IRCTC Online Passenger R 🖻                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Suggested Sites 👻 😰 Web Sice Gallery 👻                                                                           |                              |                  |                               |

| Net Lab Server 🖉 SUPREM 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                  |                              | 🖄 • 🖾 • 📾 👼      | ▼ Page ▼ Safety ▼ Tools ▼ 😥 ▼ |

| UPREM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                  |                              |                  |                               |

| TIT TEST FOR THE SUBL PROBAM - WHN TRANSIST<br>ID DYSI-0.005, DFUH-0.5, MARK-0.8<br>255 ORNT-111, ELEM-35, CONC-1216<br>DEL MARK-MEGO, DSCH-2.019<br>ELIM HEAD-Y<br>DO TYTE-SUBL, DIME-60, TEMS-900, MODL-DSYO<br>DT TYTE-SUBL, DIME-60, TEMS-900, MODL-DSYO<br>DET TYTE-SUBL, ILEM-25, AREY-30, DOSE-7E15, N<br>TET TYTE-SUBL, ILEM-25, AREY-30, DOSE-7E15, N<br>TET TYTE-SUBL, ILEM-25, AREY-30, DOSE-7E15, N<br>TET TYTE-SUBL, ILEM-25, TEMS-1000, MODL-NITO,<br>LET TYTE-SUBL, ILEM-25, TEMS-1000, MODL-NITO,<br>TET TYTE-SUBL, ILEM-1, TEMM-1000, MODL-NITO,<br>TET TYTE-SUBL, TIME-3, TEM-1000, MODL-NITO,<br>TET LIME-5, TEMS-1, TEM-1000, MODL-NITO,      | 00L-HB01<br>H00L-HB01<br>M00L-HB01<br>M00L-HB01                                                                  |                              |                  |                               |

| ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                              |                  |                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | G RESULT                                                                                                         |                              |                  |                               |

| RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IRANSISTOR -<br>DL-DRYO<br>~TE13, MODL-MED01<br>244215, MODL-MED01<br>DL-MITO, MODL-MED01<br>DL-MITO, MODL-MED01 |                              |                  |                               |

| D<br>SUN<br>SELECT ALL AND COPY THE FOLLOWIN<br>1TILL IEST FOR THE SUBI PROGRAM - NEW<br>2GRID DWIT=0.05, PTHM-0.5, YMAX-MC<br>3SUBS ORNT=111, ELEM-8, CONC-114<br>4NOCH MARY-MOID, DNOR-2.OFB<br>5STEP TYPE=NEN, ELEM-8, AKEV-30, DOSE<br>9STEP TYPE=NEN, ELEM-8, AKEV-30, DOSE<br>10STEP TYPE=NEN, ELEM-8, TEMP=1000, MO<br>11FRIMT HEAD-7, TOTI-7<br>13STEP TYPE-OKID, TIME-1, TEMP=1000, MO<br>14STEP TYPE-OKID, TIME-1, TEMP=1000, MO<br>14STEP TYPE-OKID, TIME-1, TEMP=1000, MO<br>15STEP TYPE-OKID, TIME-1, TEMP=1000, MO<br>15STEP TYPE-OKID, TIME-1, TEMP=1000, MO<br>15STEP TYPE-OKID, TIME-1, TEMP=1000, MO<br>15STEP TYPE-OKID, TIME-1, TEMP=1000, MO | IRANSISTOR -<br>DL-DRYO<br>~TE13, MODL-MED01<br>244215, MODL-MED01<br>DL-MITO, MODL-MED01<br>DL-MITO, MODL-MED01 |                              |                  |                               |

Figure 2. Process simulation (output page) using SUPREM.

### 2.2 Device Simulation using BIPOLE

Shrinking device dimensions approaching atomic dimensions and new device designs utilizing band-gap engineering give rise to many new and previously unknown effects in the electrical, mechanical and thermal behavior of the devices. It is a time-consuming and expensive task to investigate these effects through real fabrication experiments, and therefore simulation has become increasingly popular. The critical internal device quantities, such as the current flow, electrical field, carrier density, and temperature distribution are not measurable and can only be accessed through device simulation.

Device simulation is used for obtaining the device characteristics, for example, static, timedependent, large and small-signal frequency-dependent behavior of semiconductor devices, their electrical behavior and also the SPICE parameters. SPICE parameters are subsequently used in circuit simulation. Device simulation models the electrical, optical, mechanical and magnetic behavior of semiconductor devices using structures obtained from process simulation. Advanced multidimensional process and device simulation calls for models that are comprehensive and physically based. However, this task is usually difficult to achieve, since the physics of many of the processes of interest is highly complicated. In such cases, an alternative is to use empirically based macroscopic models, with parameters chosen that are related to experiment. Both complex and computationally intensive first principle models, as well as simple and empirically based models, play important roles in the simulation of semiconductor-related phenomena. Empirically based models, although limited in scope, are attractive because they are less computationally intensive than first principle models.

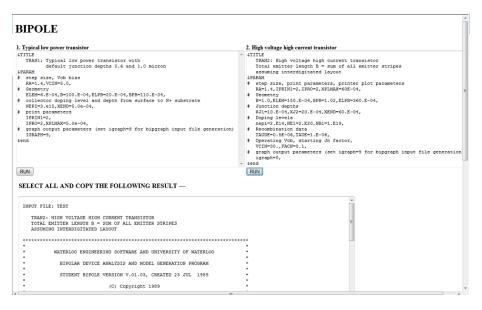

Figure 3. Device simulation (output page) using BIPOLE.

BIPOLE [3] is a quasi-two-dimensional device simulator, developed at the University of Waterloo, Canada, which specifically focuses on rapid prediction of terminal electrical characteristics of bipolar transistors. Program input comprises fabrication data such as mask dimensions, impurity profiles and physical parameters such as carrier lifetime. The calculation is based on the variable boundary regional approach using one-dimensional transport equations. Two-dimensional and quasi-cylindrical edge effects are handled by combining the vertical one-dimensional analysis with a coupled one-dimensional horizontal analysis of the transport equations in the base region. It is then used to solve the transport equations for diffusion and drift in the presence of arbitrary recombination in quasi-neutral regions. This scheme is extremely fast in terms of computing time. BIPOLE can also be used for accurate avalanche

multiplication and breakdown studies in high-speed transistors with shallow collector regions and heterojunction structures, including graded base Ge mole fraction in SiGe devices, and emission across the thin interfacial oxide layer in a poly-Si emitter and offers a facility for automatic parameter extraction for SPICE models. PISCES, developed at Stanford University was the first successful general-purpose two-dimensional device simulation program applicable to any arbitrary semiconductor device, whether its dominant mode of operation was MOS or bipolar. Since the early 1980s commercial vendors such as SILVACO and Synopsys have developed their own graphical user interfaces (GUI) around existing frameworks, which facilitated the integration of process and device simulation tools by non-specialists within a wider engineering environment. The concept of general purpose process and device simulators that allows flexible simulation of different structures in different technologies became a reality. In the proposed simulation laboratory we use BIPOLE and the device simulation run sheet for a high voltage bipolar transistor is shown in Figure 3. The process and device simulation modules implemented in the online laboratory were also used for home assignments for theory subject.

### 2.3 Evaluation

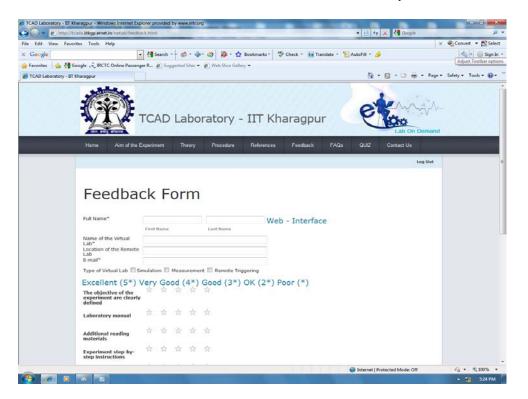

For the evaluation and study the effectiveness of the laboratory, a survey form was prepared, which contains short questions relating to: i) effectiveness of modules, ii) accessibility of the modules and online laboratory manual, iii) how it helped clarifying concepts, iv) stimulate student interest in solving home assignments and laboratory, and v) organization of the modules. The questions were answered on a scale of Excellent, Very Good, Good, OK and Poor. The participation in the survey was voluntary and anonymity of the students was maintained to gain an unbiased opinion. Students were also asked to give their opinion (feedback) about modules and online laboratory. Figure 4 shows the screenshot of such a feed back page. As the TCAD laboratory is available on the web; comments were also received from students and teachers from other universities. The feedback data obtained shows an increasing interest of the students to the online laboratory. Following are some sample excerpts of the students feedback collected from comments section of the survey form:

Figure 4. Technology CAD laboratory feedback form for students response.

"The modules helped me a lot. The modules are better than conventional simulation laboratory because it showed sequence of IC processing and also could be used at any time."

"Very helpful in introducing the process/device simulation and concepts involved with IC fabrication."

## 3. Conclusion

Student's feedback through evaluation survey was obtained to determine the impact of the laboratory modules on student learning and to improve teaching of the microelectronics course. Students greeted the technology CAD laboratory with enthusiasm and overwhelmingly. Online laboratory enables students to access the laboratory at their own time and pace outside the classroom and laboratory. The proposed laboratory is expected to be an aid for microelectronics teaching and also expanding the laboratory education.

## References

- 1. G. A. Armstrong and C. K. Maiti, "TCAD for Si, SiGe and GaAs Integrated Circuits", The Institution of Engineering and Technology (IET), UK, 2008.

- 2. SUPREM II, User manual.

- 3. BIPOLE, User manual.