# Incorporating Nanoscale System Design into the Undergraduate Electrical and Computer Engineering Curriculum

Ridha Kamoua, Donghwi Kim, Glenn Roach Department of Electrical and Computer Engineering, Stony Brook University, Stony Brook, NY 11794-2350 <u>ridha@ece.sunysb.edu</u>

Abstract - This paper reports on an effort at Stony Brook University to introduce basic concepts of nanotechnology and Computer into the Electrical Engineering undergraduate curriculum with particular emphasis on circuit and system design issues. The approach taken consists of weaving nanoscale material into existing courses rather than developing complete new courses. Specifically, material is introduced into an introductory semiconductor course at the device level; a 3-week instructional module is incorporated into an existing course on Digital Integrated Circuits at the circuit and system level; and nanoscale projects are proposed to and undertaken by students as part of their capstone senior design project or undergraduate research. Initial results indicate that students were very much interested in the emerging nanotechnology field and a number of them participated in summer research for undergraduate students at Stony Brook as well as other universities and research centers.

*Index Terms* – nanotechnology, electrical and computer engineering curriculum, system design, nanoscale module.

## **1. INTRODUCTION**

The scientific community widely recognizes that the science and engineering of materials and devices at the nanometer scale will be one of the dominant fields of research and development during the next few decades. Within the context of electrical and computer engineering, a rapid transition from microelectronics to nanoelectronics is already occurring. The well-known Moore's Law [1] predicts the doubling of computer performance every 18 months or so. For decades, the industry has fulfilled Moore's prophecy by shrinking the dimensions of the elementary devices in order to pack more devices per silicon area and increase their intrinsic performance. It has been predicted several times that silicon would soon reach its ultimate limits, and that eventually some other technology would have to be found.

Various nanoelectronic device candidates for replacing silicon technology have already been proposed [2-11]. Courses on nanoelectronics are also being introduced in the undergraduate curriculum at various universities. However, relatively little attention is being devoted to the design aspects at the circuit and system level. The experience with complementary metaloxide-semiconductor (CMOS) technology has shown that Moore's law is as much a result of design improvements as of progress in the physical sciences, which means many improvements have come from progress in logic and circuit design. Therefore, to tap the potential of nanosystems five or ten years in the future, it is necessary to educate engineers in nanosystem design to appreciate the potential of nanotechnology, and to take advantage of it.

This paper presents an approach for introducing designoriented nanotechnology into the existing undergraduate electrical and computer engineering curriculum at Stony Brook University. Section 2 reviews the existing curriculum, section 3 outlines the changes proposed and carried to introduce nanotechnology. Section 4 describes a three-week module incorporated into an existing course on integrated electronics, Section 5 considers the proposed curriculum changes in relation with the ABET requirements. Finally, section 6 presents a summary of the paper.

### 2. EXISTING CURRICULUM

The Department of Electrical and Computer Engineering offers two ABET accredited programs – one in electrical, the other in computer engineering. Both programs require

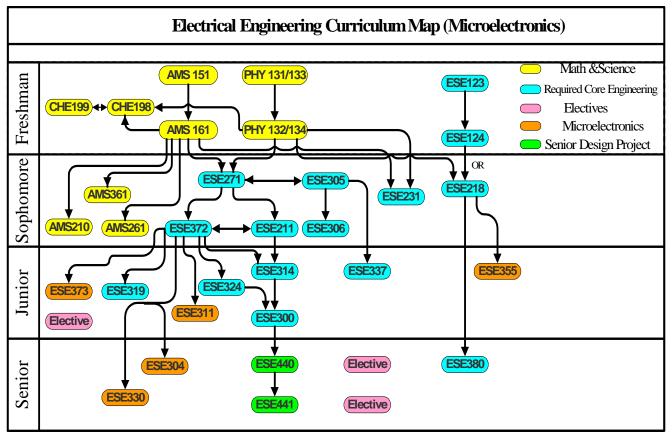

FIGURE 1

CURRICULUM MAP FOR THE MICROELECTRONICS SPECIALIZATION IN THE ELECTRICAL ENGINEERING PROGRAM

students to take a number of courses that involve the design of electronic systems both digital and analog. As an illustration, figure 1 shows the curriculum map for the microelectronics specialization under the electrical engineering program. After the sophomore year, students complete the basic circuits, electronic devices, and discrete electronic circuits. During the junior and senior years, students take more advanced courses in integrated circuits such ESE 311 (Analog Integrated Electronics), ESE 330 (Digital Integraed Electronics), and ESE 355 (VLSI Design). These courses are also taken by computer engineering students as technical electives. As common in most engineering programs, these type of courses are based on CMOS technology.

### **3.** APPROACH

As described in section 2, undergraduate students in electrical or computer engineering programs at Stony Brook are hardly exposed to the emerging field of nanosclae devices and circuits. To update the curriculum, two approaches could be adopted 1) introduce new courses in nanoscale system design, or 2) incorporate such material within existing courses. We have chosen the latter approach for two reasons: 1) it is easier to add material to existing courses compared to adding complete new courses as the curriculum already requires a large number of courses to be taken, 2) nanoscale system design is not a mature field and considerable research still needs to be done. The approach adopted was to incorporate material on nanoscale design in the following courses:

- 1. ESE 231: Introduction to Semiconductor Devices

- 2. ESE 330: Digital Integrated Electronics.

- 3. ESE 440/441: One year design project required for seniors

- 4. ESE 499: Undergraduate research

Introduction of nanotechnology in the semiconductor device course were described in an earlier paper. Here, the focus is on the module developed and introduced in the digital integrated electronics course.

The electrical and computer engineering programs have strong curricula in digital circuits and systems. In particular, we offer two separate courses in CMOS digital design: ESE 330 Integrated Electronics and ESE 355 VLSI System Design. While VLSI System Design emphasizes a high-level design picture, ESE330 focuses on the transistor level, and is an ideal testing field of introducing new concepts in circuit design. This 3-credit course deals specifically with circuit-related issues in digital design, such as the relative merits of different logic families, issues of signal integrity, analog-like building blocks

## San Juan, PR

such as sense amplifiers, memory arrays, etc. Due to the complementarity with ESE 355, there is a great freedom in the choice of topics.

ESE330 is offered every year in the fall semester. Enrollment is typically around 40-50 students (out of about 300 EE/CE majors). It should be noted that, while ESE330 is a course targeting electrical engineering and computer engineering majors, it is also regularly attended by undergraduates from other majors, such as Engineering Science, Mechanical Engineering, Mathematics, and occasionally by humanities students. The introduction of an innovative, cross-disciplinary module will make it even more attractive to non-ECE students: especially to Physics and Chemistry majors, as well as for any undergraduates who want to acquire a concrete feel for the possibilities for nanotechnology.

ESE330 was chosen as a spearhead for introducing nanotechnology into the ECE curriculum, a three-week instructional module was developed and woven into the course. Currently, ESE330 is a junior- or senior-level course. However, there is no reason why younger students could not be exposed to the same materials. The only prerequisites for understanding the materials presented in the nanosystem module are a basic knowledge of electrical circuits, and use of circuit simulation software. Within the Stony Brook curriculum, students could easily take on a project in nanoscale circuit design while in their sophomore year. As the educational material matures, the basic concepts of nanosystem design, with a simplified circuit design component, could be moved to a freshman course such as ESE123 Introduction to Electronic Design.

In addition to changes in the introductory course on semiconductor devices and the incorporation of a module in the integrated electronics course, students are exposed to the design process with novel nanoscale devices in their senior design project as well as undergraduate research.

## 4. MODULE ON NANOSCALE SYSTEM DESIGN

The proposed three-week instructional module has the goal of educating ECE majors in the fundamentals of nanoscale devices and circuits. Of course the material will include some elements of the physics, chemistry, and materials science aspects of nanotechnology. However, this introduction has the primary purpose of letting students appreciate the fundamental differences between microsystems and nanosystems, not only regarding their physical nature (which is often secondary to a circuit or systems designer), but in terms of the main figures of merit of any electronic design: speed, power, reliability, and cost. Therefore, as is often done in engineering, the physical complications will be abstracted out, to highlight design principles. On the other hand, to abstract does not mean to neglect. Particular attention will be paid to implications of the physical structure on circuit and system performance, such as device operation, defect tolerance, and interconnect delay, etc.

The outline of the course with the introduced module on nanoscale design, as offered in fall 2005, is:

## 1. Introduction to Deep Submicron Digital IC Design

- Brief History of IC Industry

- MOS Transistor Structure and Operation

- CMOS versus NMOS

- CAD Tools

## 2. MOS Transistors

- Structure and Operation

- MOS Capacitor

- Threshold Voltage

- Current-Voltage Characteristics

- Velocity-Saturated Current Equations

- Subthreshold Conduction

- Capacitances of MOS Transistor

## 3. Fabrication and Simulation

- IC Fabrication Technology

- Modeling of MOS Transistors

## 4. MOS Inverter Circuits

- Voltage Transfer Characteristics (VTC)

- Noise Margins

- Resistive Load Inverter

- Linear and Saturated Enhancement Load Inverters

- CMOS Inverters

- Pseudo NMOS Inverters

- Sizing of Inverters

## 5. Static MOS Gate Circuits

- CMOS Gate Circuits

- Power Dissipation in CMOS Gates

## 6. Interconnect Design and Switching Time Analysis

- Interconnect RC Delays

- Interconnect Coupling Capacitance

- Delay Calculation

## 7. Dynamic Logic Design

- Pass Transistors

- CMOS Transmission Gate Logic

## 8. Memory Design

• CMOS Static Memory

## 9. Nanoscale Devices and Modeling

- Wave Nature of electrons (Particle-Wave Duality)

- Quantum Tunneling

- Solid State Nanoelectronic Devices

- Resonant Tunneling Devices (RTD)

- Single Electron Transistor

- Quantum DOT

- Molecular Nanoelectronic Devices

- MOSES, SIMON, QCADesigner, etc.

## 10. Nanoscale Architectures, Modeling and design

- Crossbar

- CMOL

- Quantum Cellular Automota (QCA)

The instructional module on nanoscale design corresponds to topics 9 and 10 in the outline. It consists of four components (each component corresponds to roughly one week of instruction):

**Component 1:** Review of CMOS scaling of the last decade and analysis of the limits of device scaling and proposed solutions. For this purpose, the textbook [12] selected for the course emphasizes deep submicron CMOS technology where the MOSFET can be considered as a nanoscale device.

**Component 2:** Basic concepts and description of nanoelectronic devices. Since ESE 330 requires only a basic electronics course as a prerequisite, important concepts in quantum mechanics needed to be introduced. In particular the particle-wave duality and quantum tunneling are very important. In fact, a quite number of the proposed nanoscale devices exploit the tunneling process as a principle for their operation. Such devices include Single Electron Transistors (SETs) [13], Resonant Tunneling Devices (RTD), and quantum dots. In addition, the tunneling mechanism is also relevant to the nanoscale MOSFET, however in this case it negatively effects the performance of the device. Other nanoscale devices considered include: nanowires and nanotubes [15], Carbon Nanotube Transistors (CNTs) [9], and molecular devices[16].

**Component 3:** CMOS Integrated circuit design is centered around the intelligent use of computer aided design (CAD) software tools. Schematic capture, layout editing, circuit and logic simulation allow students to verify the accuracy of their hand design and, even more importantly, observe the detailed behavior of the circuit and develop a feel for it. Circuit simulation has been shown to usefully complement experimental lab work, and the large majority of today's electronics textbooks rely on software simulation such as SPICE (Simulation Program with Integrated Circuits Emphasis) to illustrate design concepts, even more than on actual bench work.

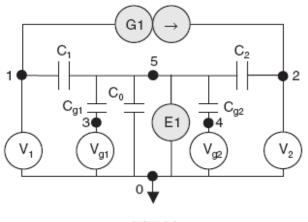

Similarly, designing nanoscale circuits and systems requires the use of modeling and computer aided design (CAD) tools. The electrical model or available simulation tools for the nanoscale devices listed under Component 2, are introduced. A number of simulation tools are available free of charge from <u>http://www.nanohub.org</u>. In particular, students can simulate the tunneling process through single and multiple energy barriers as well as the current–voltage characteristics of resonant tunneling diodes. These tools are available online and don't require installation by the student. For circuits based on single electron transistors, three methods are available simulating these devices: Monte Carlo based methods (MOSES, SIMON,...), direct solving of a master equation, and macromodeling in SPICE (Simulation Program with Integrated Circuits Emphasis). The last approach was adopted as students use SPICE for the simulation of CMOS circuits. An example of a SPICE macromodel [18] for the single electron transistor is illustrated in figure 2.

FIGURE 2 SINGLE ELECTRON TRANSISOR SPICE MACROMODEL

QCADesigner (http://www.qcadesigner.ca/) is a simulation tool for the design and simulation of Quantum Dot Cellular Automata (QCA). It is available free of cost for academic use. QCADesigner facilitates rapid design, layout and simulation of QCA circuits by providing powerful CAD features available in more complex circuit design tools.

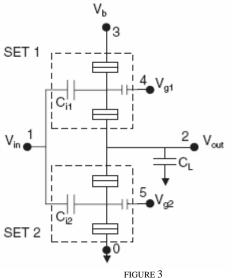

**Component 4:** Design problems and projects using the nanodevices and tools described earlier were assigned to students. The first design problem was related to the basic inverter using single electron transistors. As described in the course outline under topic 4, students are exposed to the analysis and design of MOS inverters. Therefore simulating the single electron transistor inverter enables students to compare the merits of the two approaches. Students were asked to plot the SET current voltage characteristics similar to the MOSFET characteristics based on the model in figure 2. Students were then asked to characterize a SET inverter illustrated in figure 3 in terms of delay time and dynamic and static power consumption.

## San Juan, PR

INVERTER BASED ON SINGLE ELECTRON TRANSISTORS

Finally, students were asked to simulate a ring oscillator using three inverters to determine the oscillation frequency.

Another problem requires the design of a majority gate and a full adder based on Quantum dot Cellular Automota (QCA). QCA is an emerging nanotechnology concept for the realization of a computer built with arrays of nano-scale QCA cells. These QCA cells are capable of performing any complex computational function. Students were given a tutorial on QCADesinger, which was used for simulating these two circuits.

### 5. Relation to ABET Requirements

The undergraduate program in electrical and computer engineering at Stony Brook university is an ABET accredited engineering program. The proposed changes to the existing curriculum will contribute to the fulfillment of ABET's criterion 3, in particular:

## b. An ability to design and conduct experiments, as well as analyze and interpret data.

In modern electrical engineering, designing and analyzing a 'simulated experiment' in software is perhaps as important as physical lab work. Even when the individual devices are well characterized, still the behavior of the circuit as a whole is not necessarily understood. Moreover, computer simulation provides access to internal quantities that would not be visible in a physical laboratory. In the context of a new, largely unexplored discipline such as nanosystem design, where no established design techniques exist, students are basically on their own and will obtain precious experience in the design of focused experiments to assess the capabilities of a given technology or device.

c. An ability to design a system, component, or process to meet desired needs within realistic constraints such as San Juan, PR

## economic, environmental, social, political, ethical, health and safety, manufacturability, and sustainability.

Future nanoscale systems will compete with mature, aggressively scaled CMOS systems. To this purpose, all designs carried out in the project will start from the figures of merit of such systems and will attempt to exceed them at least in one respect (cost, density, power consumption, etc).

## d. An ability to function on multi-disciplinary teams.

While basic classroom work will be carried out by all students homogeneously, all projects will require the division of tasks into the understanding of the chemical and materials properties of the devices under study; device operation; circuit design; and system architecture.

## *i.* A recognition of the need for, and an ability to engage in life-long learning.

From the outset, it will be made clear that the field of nanotechnology is in a permanent state of flux. Students will be exposed to the true human condition of researchers, which is one of continuous challenge and learning. It will also teach them that success is especially to be sought in those areas where there is no guarantee for it.

## j. A knowledge of contemporary issues.

Nanotechnology is widely expected to impact all areas of our lives. Rather than getting a general, popular-magazine view of the subjects, students will acquire a real feel for the potential impacts of the new technologies.

All the course and project activities will follow ABET guidelines, including the implementation of the student portfolio.

## 6. CONCLUSIONS

Extending Moore's law will require new nanoelectronic devices and design methodology. To understand and take advantage of this cutting edge new technology, an educational program with design-oriented nanoelectronics compatible with existing electrical and computer engineering undergraduate curriculum is necessary. This paper describes an instructional module for nanotechnology system design that was introduced in an existing course on digital integrated electronics. Student showed great interest in nanotechnology. A potential improvement in the delivery of the module would be to cover the material on nanoscale devices in a different course that is made a prerequisite. The developed module and technical tools will allow students to appreciate the impact of nanotechnology on their field, by extending their experience with CMOS design.

#### ACKNOWLEDGMENT

This work was supported in part by the National Science Foundation under Grant No. CCF-0407183.

#### REFERENCES

- [1] G. E. Moore, "Cramming more components onto integrated circuits," Electronics, vol.38, no.8, Apr.1965.

- [2] C. P. Collier, E. W. Wong, M. Belohradsky, F. M. Raymo, J. F. Stoddart, P. J. Kuekes, R. S. Williams, and J. R. Heath, "Electronically configurable molecular-based logic gates," Science, vol.285, pp.391-394, July 1999

- [3] J. Chen, M. A. Reed, A. M. Rawlett, and J. M. Tour, "Observation of a large on-off ratio and negative differential resistance in an electronic molecular switch," Science, vol.286, p.1550, 1999.

- [4] J. Chen, W. Wang, M. A. Reed, M. Rawlett, D.W. Price, and J. M. Tour, "Room-temperature negative differential resistance in nanoscale molecular junctions," Appl. Phys. Lett., vol.77, p.1224, 2000.

- [5] S. Tans, A. Verschueren, and C. Dekker, "Room-temperature transistor based on a single carbon nanotube," Nature, vol.393, pp.49-52, 1998.

- [6] Z. Yao, H. W. C. Postma, L. Balents, and C. Dekker, "Carbon nanotube intramolecular junctions," Nature, vol.402, pp.273-276, 1999.

- [7] T. Rueckes, K. Kim, E. Joselevich, G. Tseng, C. Cheung, and C. M. Lieber, "Carbon nanotube based nonvolatile random access memory for molecular computing," Science, vol.289, pp.94-97, 2000.

- [8] M. S. Fuhrer, J. Nygard, L. Shih, M. Forero, Y.-G. Yoon, M. S. C. Mazzoni, H. J. Choi, J. Ihm, S. G. Louie, A. Zettl, and P. L. McEuen, "Crossed nanotube junctions," Science, vol.288, pp.494-497, Apr.2000.

- [9] A. Bachtold, P. Hadley, T. Nakanishi, and C. Dekker, "Logic circuits with carbon nanotube transistors," Science, vol.294, pp.1317-1320, 2001.

- [10] V. Derycke, R. Martel, J. Appenzeller, and P. Avouris, "Carbon nanotube inter-and interamolecular logic gates," Nano Lett., vol.1, no.9, pp.453-456, Sept.2001.

- [11] [11] H. Postma, T. Teepen, Z. Yao, M. Grifoni, and C. Dekker, "Carbon nanotubes single-electron transistors at room temperature," Science, vol.293, pp.76-79, 2001.

- [12] D. A. Hodges, H. G. Jackson, R. A. Saleh, "Analysis and Design of Digital integrated Circuits in Deep Submicron Technology", 3<sup>rd</sup> edition, McGraw Hill, 2004.

- [13] K. K. Likharev, "Single-electron devices and their applications," Proc. IEEE, vol.87, no.4, pp.606-632, Apr. 1999.

- [14] Y. S. Yu, Y. I. Jung and J. H. Park, "Simulation of Single-Electron/CMOS Hybrid Circuits Using SPICE Macro-modeling," Journal of the Korean Physical Society, Vol.35, pp.S991-S994, Dec. 1999.

- [15] M. Ziegler, R. Stan, "CMOS/Nano Co-Design for Crossbar-Based

- [16] Molecular Electronic Systems," IEEE transactions on nanotechnology, Vol.2, no.4, December 2003.

- [17] Yong Chen et al., "Nanoscale molecular-switch crossbar circuits," 2003 Nanotechnology, 14, 462-468, 2003.

- [18] G. Lientschnig, I Weymann, P. Hadley, "Simulating Hybrid Circuits of Single-Electron Transistors and Field-Effect Transistors", Jpn. J. Appl. Phys., Vol. 42, 6467-6472, 2003.